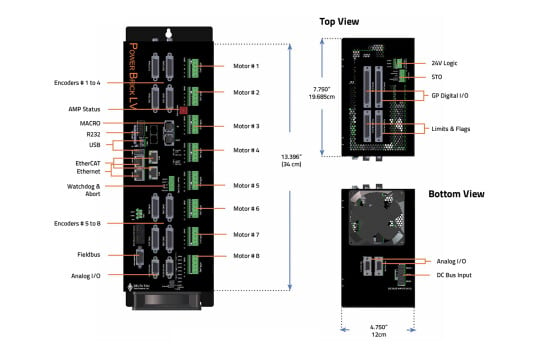

FPGA Power Brick LV

The FPGA Power Brick LV is an integrated fully scalable Machine and Motion Controller.

GET IN TOUCH ABOUT THIS PRODUCTThe FPGA Power Brick LV is an integrated fully scalable Machine and Motion Controller combining the brains of the cutting edge Power PMAC processor, the unsurpassed custom-designed Digital Signal Processor Gate3 and the low voltage brawns of the latest high performance MOSFET-based drives technology into one compact 4 or 8-axis servo package drive.

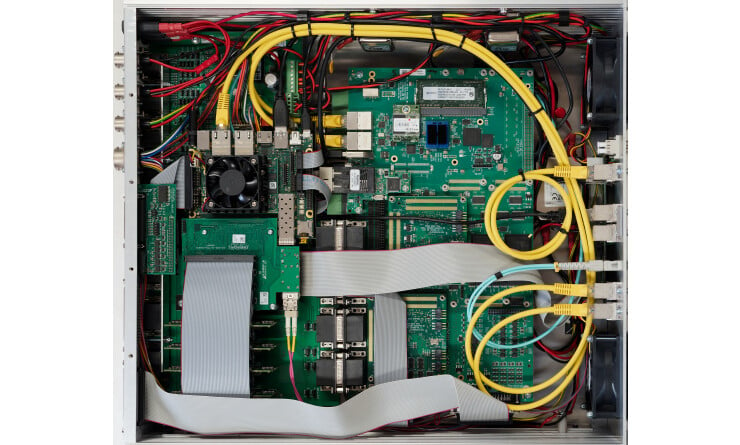

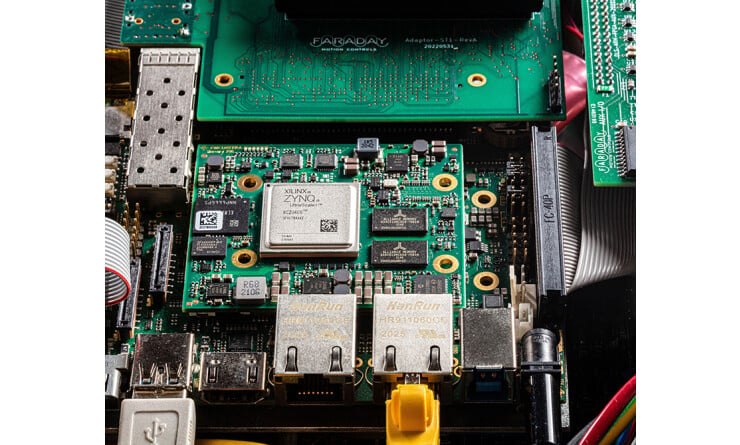

The PowerBrick LV-IMS-FPGA incorporates an FPGA based Encoder co-processor. It adds a programmable module between the back-panel connectors of a standard LV-IMS and the internal PowerBrick, intercepting the encoder data in real time.

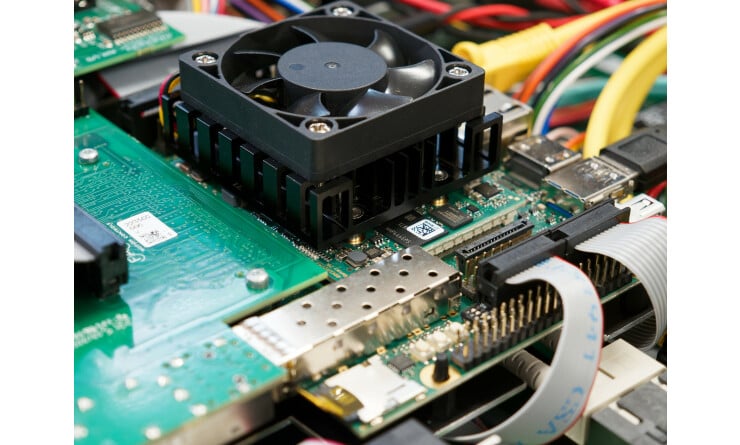

A Zynq Ultrascale+ MPSoC has been used to achieve multi-channel encoder processing for applications such as synchronizing data acquisitions with motion systems during continuous experiment scans. Individual or combinations of encoders can be used to generate multiple output triggers, and encoder position capture (of all types of encoders) can be based on those triggers.

The Zynq Ultrascale+ MPSoC has two sections, a large FPGA connected to the encode hardware, and a dual- or quad-core ARM A53 running Linux. Data can be passed between the two and to/from the Ethernet port. The FPGA is entirely user-programmable. Open-source examples will be supplied, or users with suitable FPGA programming knowledge are free to customize all sections of the co-processor as required.

Additional axes are available via MACRO (high speed fibre optic network) and/or EtherCat for a possible total of 104 (8 + 32 MACRO + 64 EtherCat) axes of centralised and coordinated motion control.

Product benefits

Five built-in control algorithms

Accurate

contouring

Position, torque,

and backlash

compensation

Multiple safety features

Download the Power PMAC PDF for a detailed overview

Product features

Control Algorithms

- Standard PID only

- PID enhanced with notch filters, deadband filters, lowpass/highpass filters, velocity loop filters, and/or trajectory prefilters

- Standard Gantry Control

- Cross-Coupled Gantry Control

- Adaptive Control

Motor Servo Control

- Extremely fast update rates (Phase and Servo)

- Standard PID with full feedforward model

- Powerful automatic tuning and analyser tools

- Analog, Pulse Width Modulated (PWM), Pulse Frequency Modulated (PFM), MACRO or EtherCAT Outputs

- Vibration suppression filters

- Multiple 7th order notch and low pass filters

- Adaptive control for varying loads

- Cascaded loops (force, height, camera auto-focus control)

- Support for custom-written commutation routines

- Support for custom-written servo routines

- Custom routines directly in

Coordinate Systems

- Up to 256 axes of coordinated or independent motion

- Up to 128 independent coordinate systems

- Up to 32 independent axes per coordinate system

- Dynamic axes transformations (e.g. offsets, rotations, mirroring)

- Forward/Inverse kinematics for nonlinear mechanisms

- User defined routines convert between tool tip coordinates and actuator positions

- Permit

Programmable Logic Control (PLCs)

- Access to all registers

- Trigonometric, transcendental, vector and matrix functions

- 64-bit floating-point architecture optimized math

- Executive functions for standalone operation

- Data gathering of up to 128 hardware/ software registers per servo cycle

- Program in PMAC Script

- Program in ANSI C:

- Real time with pre-emptive kernel routines

- General purpose routines

- MATLAB®/Simulink® Embedded Coder® generated code

Electronic Gearing and Cams

- Powerful master/slave techniques

- Position following (gearing) requires no program for motion

- External time base (cam) keeps full trajectory flexibility (non-returning, limited reversal, e.g. moving web application)

- Up to 256 cam tables (16k points each)

- Position/torque profile(s)

- Returning, forward/reverse travel

- Extremely precise synchronized outputs

Trajectory Generation

- Auto-coordination of multiple sets of axes

- Linear, circular, rapid, position-velocitytime (PVT), LIN to PVT (curve fit), Spline move modes

- Seamless blending between linear, circular and PVT modes

- Automatic move until trigger (hardware input)

- True S-Curve accel / decel

- All move modes supported with user kinematics

- Dynamic multi-block lookahead with velocity/acceleration control and jerk limit

- Sub-millisecond segmentation time

- Negative feedrate for true motion reversal in lookahead

- Move block execution rate up to 10,000 blocks/sec

- G-code, M-code, and T-code ready

- Calculations and I/O synchronous to motion

- Tool radius compensation, 2D or 3D

Compensation Tables

- Position/torque compensation tables in 1D, 2D, or 3D with rollover and mirroring options

- 1st/3rd order interpolation between points every servo cycle

- Up to 256 compensation tables (64K each)

- Support for superimposed compensation table results

- Backlash compensation, fixed or in tables Hardware Position Capture and Compare

- Specialised circuitry tying encoder counts to digital I/O

- I/O on exact count (w/sub-count interpolation) at any speed (within 10 nanoseconds)

- For probing, registration, measurement trigger, laser firing

Gantry Control

- Follower motor(s) executes leader’s trajectory

- Automatic skew removal on homing

- Automatic gantry cross-coupling servo correction

Safety Features

- Hardware and software over-travel limits

- Amplifier enable/fault handshaking

- Following error limits

- Integrated current limit

- Encoder loss detection

- Watchdog timer and relay for safely stopping the machine if the controller freezes.

MATLAB®’s Simulink® with Power PMAC Facilitates user-servo code generation for Power PMAC using Simulink®’s Embedded Coder (previously known as Real-Time Workshop). The objective is to fully automate code generation for Power PMAC’s servo loop closure routines (tasks) utilising Simulink’s® control blocks.

Connector layout